Здесь был вставлен Flash-объект. К сожалению, на данный момент его автоматическая обработка при конвертации в FB2 не поддерживается. Вы можете просмотреть оригинальную версию статьи здесь.

Путеводитель по процессорам Intel Sandy Bridge (часть 1)

В предыдущем 'Путеводителе по новым процессорам Intel', опубликованном примерно год назад, мы говорили о микроархитектуре Nehalem, пришедшей на смену Core в конце 2008 года. В этом обзоре речь пойдёт об архитектуре Sandy Bridge, которая в самое ближайшее время должна полностью заменить Nehalem.

На сегодняшний день чипы на базе Sandy Bridge представлены во всех линейках процессоров Intel, включая серверные Xeon, дестопные и мобильные Core i3/35/i7, Pentium и Celeron и «экстремальные» Core i7 Extreme. Незадолго до публикации этой статьи, 22 мая 2011 года, были представлены ещё семь новых процессоров на основе Sandy Bridge.

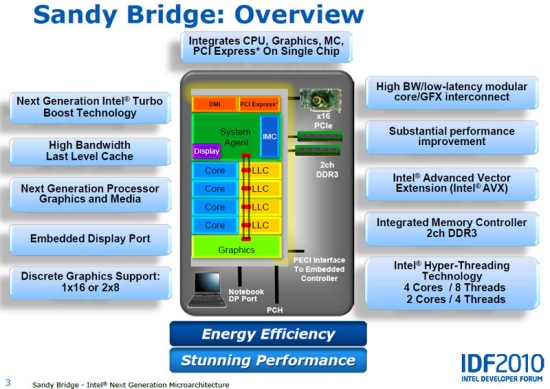

В чём же заключаются принципиальные отличия Sandy Bridge от Nehalem и в чём состоят особенности и преимущества новой микроархитектуры Intel? Вкратце эти отличия таковы: обновлённое графическое ядро в составе «системного агента» расположено на одном кристалле с вычислительным, предусмотрены новый буфер микрокоманд L0, разделяемый кэш L3, модернизированная технология Turbo Boost, расширенный набор инструкций SIMD AVX и переработанный двухканальный контроллер оперативной памяти DDR3 1333 МГц. Вместе с новой архитектурой появился и новый процессорный разъём LGA 1155.

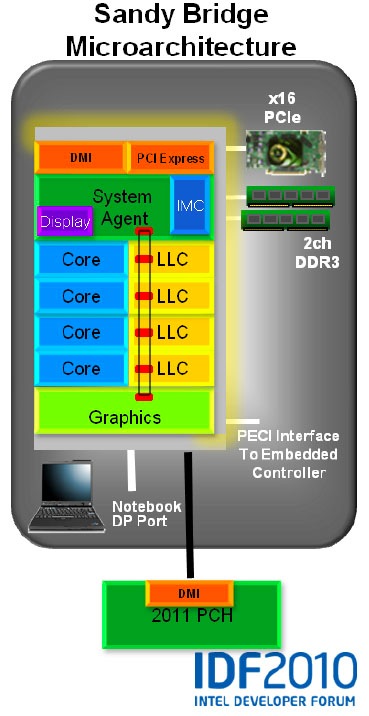

Одно из главных конструктивных отличий Sandy Bridge от Nehalem — размещение вычислительных ядер и северного моста (системного агента) на одном кристалле. Напомним, что в Nehalem сам ЦП и северный мост располагались под общей крышкой, но фактически размещались на самостоятельных чипах, которые, к тому же, были выполнены по разным технологическим нормам: ЦП — по 32-нм, а северный мост — по 45-нм. В Sandy Bridge это единый кристалл, выполненный по 32-нм техпроцессу, на котором находятся вычислительные ядра, графическое ядро, контроллеры оперативной памяти, PCI Express, электропитания (Power Control Unit, PCU) и блок видеовыхода.

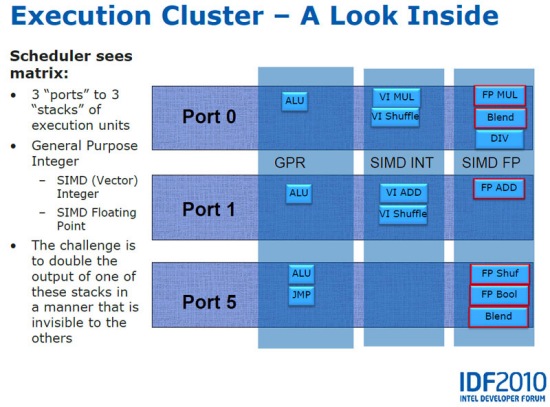

Новый набор SIMD-инструкций в чипах Sandy Bridge получил название AVX — Advanced Vector Extensions, то есть «расширенные векторные инструкции». Фактически это очередное поколение SIMD- инструкций (Single Instruction, Multiple Data — «одиночный поток команд, множественный поток данных» SSE5, альтернативная набору x86, разработанному в AMD. Разрядность регистров XMM в инструкциях AVX увеличен вдвое с 128 до 256 бит, появились 12 новых инструкций с поддержкой четырёхоперандных команд. Поддерживаются технология аппаратного шифрования Advanced Encryption Standard (AES) и система виртуализации Virtual Machine Extensions (VMX).

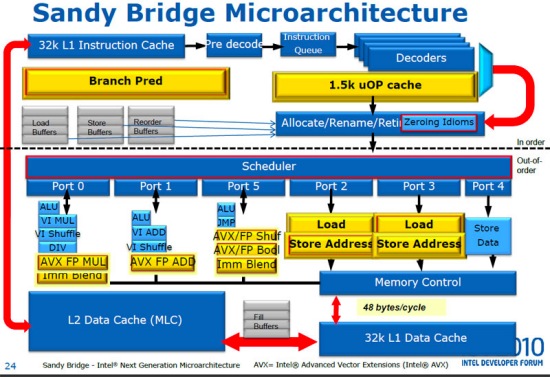

Несмотря на схожую конструкцию, у чипов Sandy Bridge больше исполнительных блоков, чем у Nehalem: 15 против 12 (см. блок-схему). Каждый исполнительный блок подключён к планировщику инструкций через 128-битный канал. Для выполнения новых инструкций AVX, содержащих 256-разрядные данные, одновременно используются два исполнительных блока.

Чипы Sandy Bridge cпособны обрабатывать до четырёх инструкций за такт благодаря четырём декодерам, встроенным в блоки выборки команд. Эти декодеры преобразуют инструкции x86 в простые RISC-подобные микроинструкции.

Важнейшее нововведение в процессорах Sandy Bridge — это так называемый «кэш нулевого уровня» L0, в принципе отсутствовавший в процессорах предыдущего поколения. Этот кэш способен хранить до 1536 декодированных микроинструкций: его смысл заключается в том, что когда исполняемая программа входит в кольцевой цикл, то есть повторно выполняет одни и те же инструкции, не требуется заново декодировать одни и те же инструкции. Такая схема позволяет заметно повысить производительность: по оценкам специалистов Intel, L0 используется в 80% машинного времени, то есть в подавляющем большинстве случаев. Кроме того, при использовании L0 отключаются декодеры и кэш- память первого уровня, а чип потребляет меньше энергии и выделяет меньше тепла.

В связи с появлением в чипах Sandy Bridge «кэша нулевого уровня» часто вспоминают трассировочный кэш (trace cache) «ветеранов гонки гигагерц» — процессоров Pentium 4 на базе архитектуры NetBurst. Между тем, эти буферы работают по-разному: в трассировочном кэше инструкции записываются точно в таком порядке, в каком они исполнялись, поэтому в нём могут несколько раз повторяться одни и те же инструкции. В L0 хранятся единичные инструкции, что, разумеется, более рационально.

Претерпел заметные изменения блок предсказания ветвлений, получивший буфер предсказания результата ветвлений (branch target buffer) удвоенного объёма. Кроме того, в буфере теперь используется специальный алгоритм сжатия данных, благодаря чему блок способен подготавливать большие объёмы инструкций, тем самым повышая производительность расчётов.

Подсистема памяти в Sandy Brigde была также оптимизирована для работы с 256-битными инструкциями AVX. Напомним, что в Nehalem использовались выделенные порты загрузки, хранения адресов и хранения данных, привязанные к отдельным дисптчерским портам, что означает возможность загрузки 128 бит данных из кэш-памяти L1 за такт. В Sandy Brigde порты загрузки и хранения при необходимости могут изменять назначение и одновременно выступать в роли пары портов загрузки или хранения, что позволяет работать с 256 битами данных за такт.

Для связи компонентов чипа, то есть вычислительных ядер, кэш-памяти L3, графического ядра и системного агента (контроллеров памяти, PCI Express, питания и дисплея), Sandy Bridge используется кольцевая шина (ring interconnect). За основу была взята скоростная шина QPI (Quick Path Interconnect, пропускная способность до 6,4 Гбайт/с на частоте 3,2 ГГц), впервые реализованная в чипах Nehalem Lynnfield (Core i7 9xxx для Socket LGA1366), адресованных энтузиастам.

По сути кольцевая шина в Sandy Bridge представляет собой четыре 32-байных кольца: шины данных, шины запросов, шины подтверждения и шины мониторинга. Обработка запросов осуществляется на частоте работы вычислительных ядер, при этом при тактовой частоте 3 ГГц пропускная способность шины достигает 96 Гбайт в секунду. При этом система автоматически определяет кратчайший путь